Fetch 회로도

fetch는 명령어를 가져오는 과정이다.

명령어를 가져올 때, 컴퓨터는 PC (Program Counter) 라는 특별한 레지스터를 이용한다.

이 레지스터에는 현재 실행할 명령어가 메모리 어디에 담겨있는지, 그 주소값이 담겨있다.

컴퓨터가 처음 실행되면, PC는 0으로 초기화되고, 메모리 0번지에 있는 명령어를 가져와 실행할 것이다.

하나의 명령어를 실행한 이후에는, 다음 명령어를 실행하기 위해 PC 값을 4 증가시킨다. (32bit 시스템 기준)

이 과정이 점프나 분기가 없는, 순차적으로 실행되는 프로그램 기준 Fetch 의 과정이다.

이를 회로도로 그려보자.

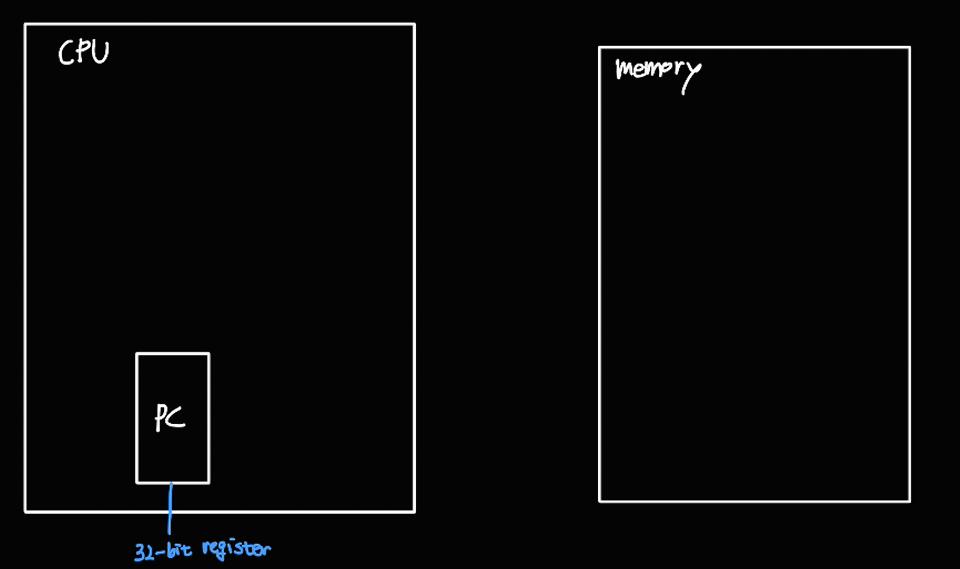

먼저 CPU 공간과 명령어를 가져오는 메모리 공간을 따로 그려보자.

CPU 안에는 PC 라는 특별한 레지스터가 있다. 32bit-register 이며 flip-flop 으로 만들어졌다고 하자.

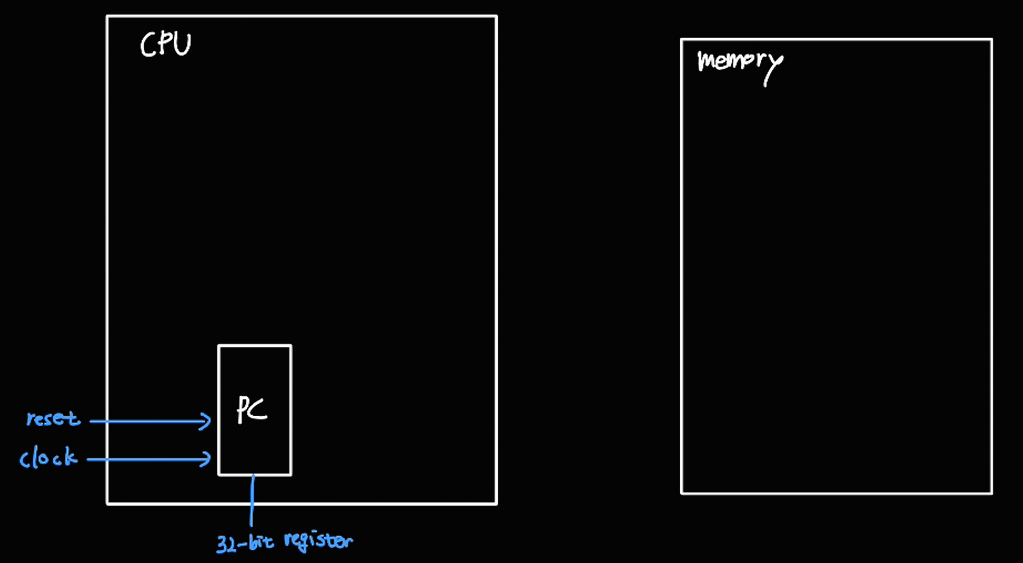

PC는 처음 컴퓨터가 실행되면 그 값이 0으로 초기화 되어야 하므로 reset 신호가 필요하다.

(실제로 MIPS는 0xBFC00000 으로 초기화하지만, 단순하게 0으로 한다고 생각하자.)

또 매 클럭 사이클마다 PC 값이 4 증가해야 하기 때문에, 클럭도 입력으로 들어온다.

두 입력신호눈 모두 1bit 입력 신호일 것이다.

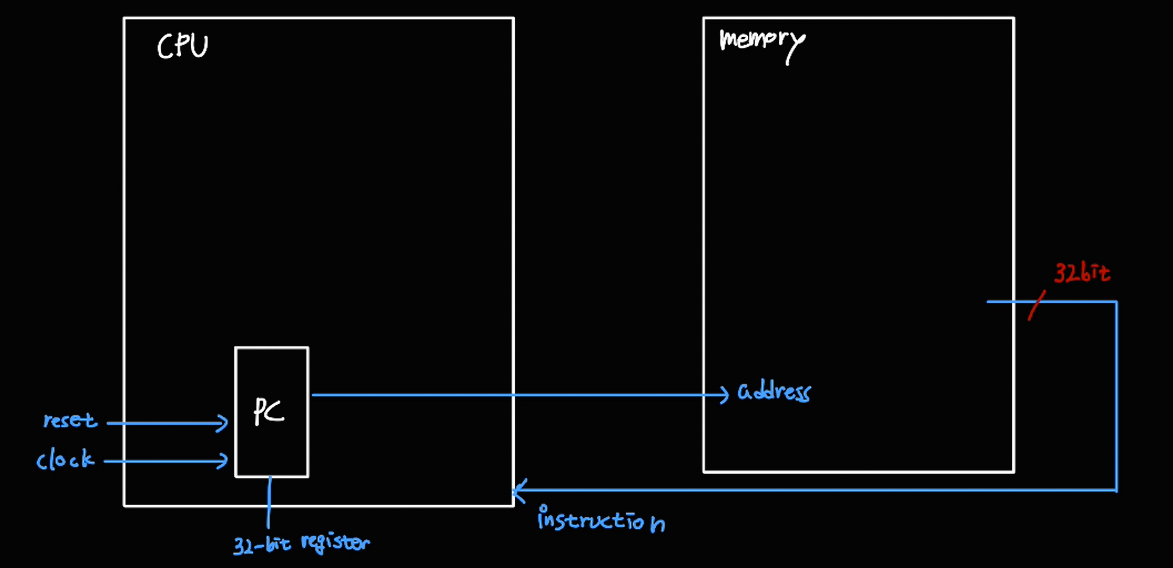

0으로 초기화된 PC는 메모리에서 그 0이라는 주소값에 있는 명령어를 읽어온다.

주소값과 출력 data는 모두 32bit 일 것이다.

지금은 fetch만 보고 있으니, 이렇게 가져온 명령어를 잘 decode 하고 execution까지 했다고 하자.

이제 프로그램 카운터의 값을 4 늘려줄 차례이다.

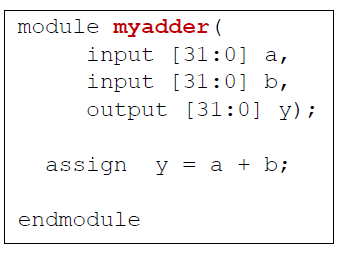

프로그램 카운터의 값을 늘리기 위해서 현재 PC 값과, 4라는 상수값을 소스로 받는 adder 룰 둔다.

이 adder의 출력은 PC의 새로운 입력으로 들어오게 된다.

이것으로 fetch 를 수행하는 회로도가 완성되었다.

여기에서 한가지 유의할 점이 있다.

지난 글에서 조합회로와 순차회로에 대해 정리했었다.

현재 CPU에 있는 add는 조합회로이다.

따라서 PC값과 4를 받아서 PC + 4 라는 값을 거의 즉시 내보낸다.

(모든 과정은 아무리 빨라도 빛보단 느리니 완벽한 즉시는 아니겠지만, 거의 즉시 발생한다.)

따라서 PC에 클럭이 들어오면 거의 즉시, PC에는 PC + 4 라는 값이 입력으로 들어오는 것이다.

하지만 PC 레지스터의 실제 값은 PC + 4 가 아니라 PC로 유지된다.

그 이유는 PC가 플립플랍으로 구성되어 있기 때문에, Clock의 rising edge 에서만 값이 바뀌기 때문이다.

따라서 클럭사이클 하나가 끝나고, 다음 클럭사이클이 들어오면, PC값은 그때 PC + 4로 업데이트 된다.

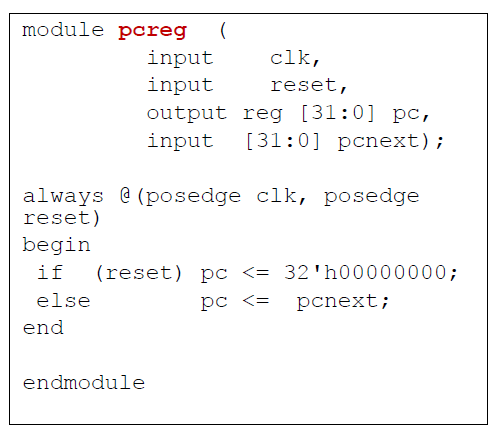

이 동작을 아래와 같은 베릴로그 코드로 짤 수 있다.

이 코드는 오직 pcreg 라는 MIPS 부품이 어떻게 동작하는지를 기술한 'behavior 모델링' 이다.

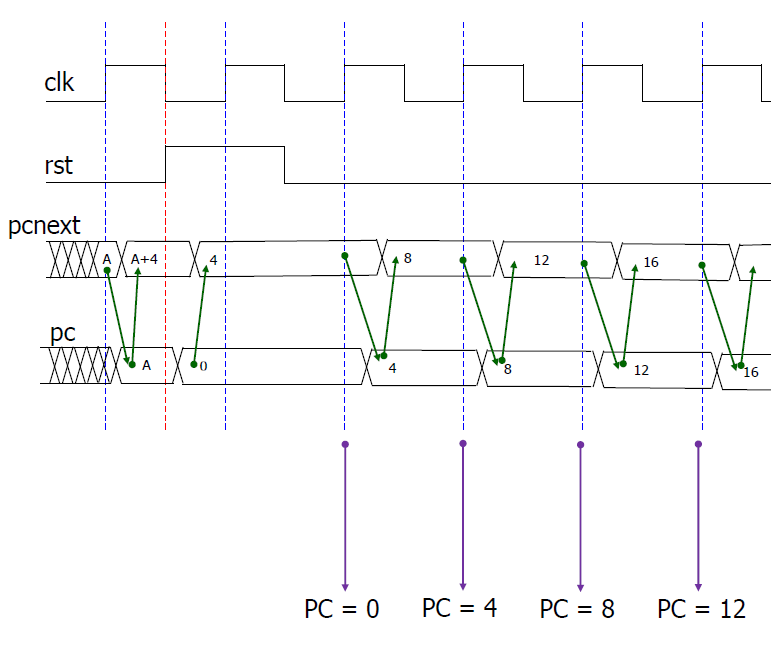

이제 이를 기반으로 PC 레지스터에 값이 어떻게 읽고 쓰여지는지 그 과정을 아래 타이밍 그래프로 함께 보자.

왼쪽부터 보자.

PC에는 처음에 어떤 값이 들어있었다고 하자.

PC next, 즉, 이후에 PC로 들어오는 input 데이터 패스에는 A 라는 값이 들어있다.

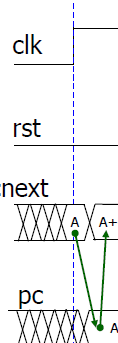

위에서 말했듯이, PC는 플립플롭으로 구성된 레지스터라, clock의 라이징 엣지가 아니면 값을 쓰지 않는다.

그래서 기존에 갖고 있는 값을 쭉 갖고 있다가 clock 의 라이징 엣지가 되면 PC next에 있는 A라는 값으로 PC를 업데이트한다.

이 업데이트는 '거의 즉시' 되지만 완벽한 즉시는 아니라서 약간의 딜레이가 존재한다.

그래서 이렇게 clk 의 라이징 엣지 (파란색 점선) 이후 약간의 시간이 흐른 뒤에 PC가 업데이트 되는 것을 볼 수 있다.

그리고 PC가 업데이트되면, PC Next까지는 데이터패스이므로 PC next의 값도 거의 즉시 A+4로 업데이트 된다.

그래서 A와 A+4 사이에도 미묘하게 시간 차이가 존재한다.

하지만 clk의 라이징 엣지가 아니니 레지스터의 값은 A로 유지된다.

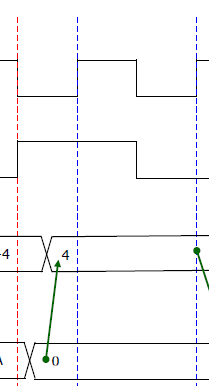

이 상황에서 만약 reset 신호가 들어오면 clock 과 상관없이 PC의 값을 0으로 바꾼다.

당연히 이 과정에도 약간의 딜레이가 필요해서 빨간 선으로 표시한 리셋 타이밍보다 약간 뒤에 0으로 초기화되는 것을 볼 수 있다.

그리고 pc에 0이라는 값이 들어왔으니 이를 기반으로 pcnext 에도 '거의 즉시' 4라는 값이 세팅되어 pc 레지스터의 input 으로 들어온다.

pc = 0, pcnext = 4라는 값은 reset 입력이 1로 유지되는동안 클럭 신호와 상관없이 쭉 유지된다.

reset 이 0이 되면, 그때부터는 클락의 rising edge 마다 PC값이 4씩 증가하는 과정이 반복된다.

모듈을 나눠서 PC 레지스터와 adder 각자의 동작만 하는 기능으로 따로 작성한 뒤, MIPS 라는 전체 시스템에 이 모듈을 가져와서 기능을 설명한다.

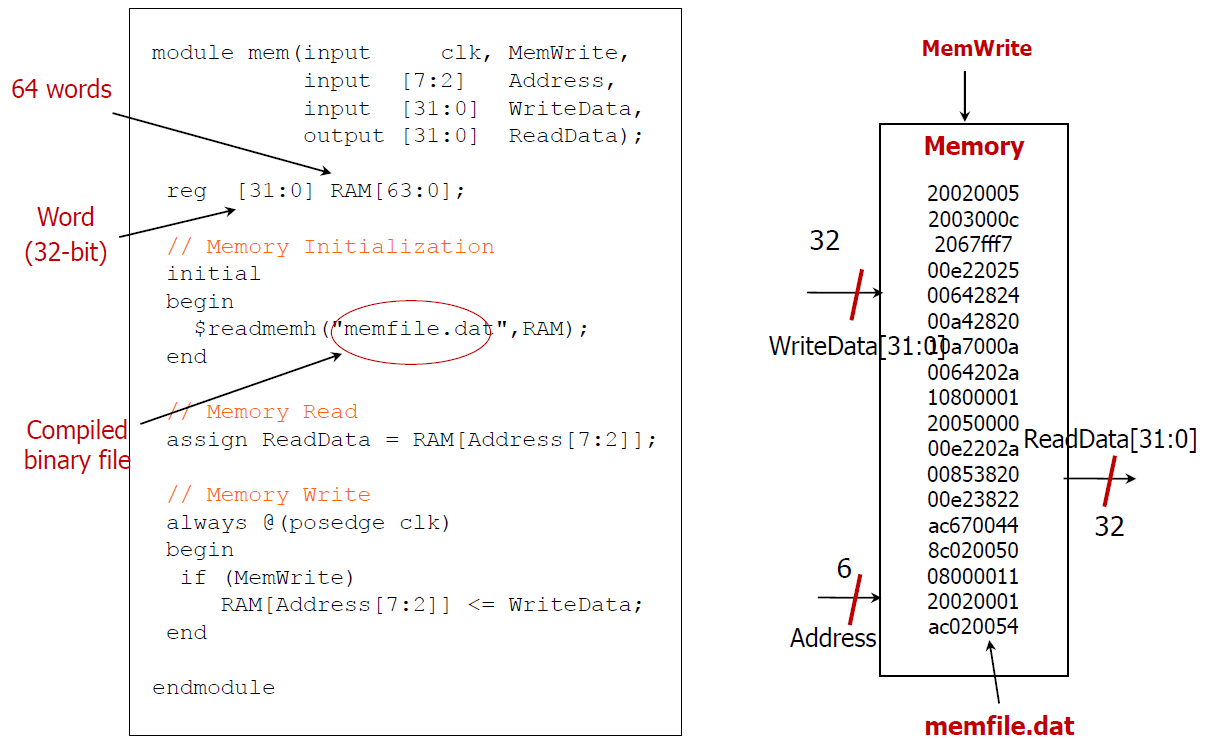

메모리에 대한 베릴로그는 위와 같다.

메모리도 다른 부품의 동작 신호에 맞춰서 값을 읽고 쓰는 동작을 해야하기 때문에 클럭이 들어간다.

메모리는 플립플롭과 다르게 라이징 엣지에 의해 쓰기를 결정하지 않고, Write Enable 신호에 의해 쓰기를 결정한다.

'CS > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 13. Single Cycle MIPS - Execute (0) | 2024.04.19 |

|---|---|

| [컴퓨터 구조] 12. Single Cycle MIPS - Decode (0) | 2024.04.19 |

| [컴퓨터 구조] 10. Single Cycle MIPS - 개요 (0) | 2024.04.18 |

| [컴퓨터 구조] 9. 곱셈, 부동 소수점 (1) | 2024.04.17 |

| [컴퓨터 구조] 8. Computer Performance (0) | 2024.04.16 |